# Passivation and characterization of hyper-uniform disordered thin-film silicon solar cells

Jelena Dolecek - 248106 -

**Master Thesis**

Master of Science and Engineering (M.Sc.)

Materials Science and Engineering

Handed in on the  $27^{th}$  of August 2021 at Institute of physics of functional complex matter (AMOLF) and Ecole Polytechnique Fédérale de Lausanne (EPFL)

**Supervisor AMOLF** Dr. Esther Alarcon Llado

**Supervisor EPFL** Dr. Anna Fontcuberta i Morral

### **Abstract**

The importance and efficiency of surface passivation for ultrathin-silicon technology with high-aspect ratio structures need to be understood and tested in order to fully explore their potential as cost-efficient, mechanically flexible and transparent solar cells. The aim of this project is to deposit, characterize and understand common passivation techniques applied on hyper-uniform disordered (HUD) structured thin-Si and eventually transfer the process on thinned-down IBC solar cells. Samples were produced with Substrate Conformal Imprint Lithography (SCIL). Electrochemical impedance spectroscopy (EIS) was implemented for Interface trap density measurements. Minority charge carrier lifetimes and absorbance data was collected for various passivation and patterning schemes on thick and thin silicon samples. An important density of interface traps states has been observed for all samples. No conclusion about the effect of different passivation approaches on the interface trap states and lifetimes could yet been drawn.

## Acknowledgments

I would like to thank Esther for giving me the opportunity to join the group and all the constructive advise during my stay. I am grateful to the whole team for the stimulating and welcoming atmosphere. Especially Daphne and Yorick, who were always available for discussions that exceeded their domain of expertise and stayed until the end. Furthermore, I'd like to acknowledge the great preliminary work accomplished by Nasim, Stefan and Alex, that made the immersion into HUD solar cells very inspiring. This collaboration was greatly supported by Albert, coordinating the collective efforts and giving me personal guidance. Thanks as well to the NanoLab, Amsterdam, staff who were supportive with training and general advise. I'm grateful to Eitan and Susan for their patient discussion about UV-VIS modifications, and generally all the collaborators at AMOLF, who make research at this institution an inclusive and collaborative experience. Work at AMOLF was great even during these special times and a feeling of belonging was transmitted from the very beginning. Further, I'm grateful to Petra Manshanden and Fatemeh Manaye from TNO, Petten, to give me valuable support for PL measurements. Last but not least, thanks a lot to Anna Fontcuberta i Morral for encouraging and supporting this project abroad regardless of the current sanitary situation.

## Contents

| Αl | bstrac | ct      |                                                                      | iii |

|----|--------|---------|----------------------------------------------------------------------|-----|

| A  | cknov  | vledgn  | nents                                                                | v   |

| C  | onten  | its     |                                                                      | vii |

| 1  | Intr   | oductio | on                                                                   | 1   |

|    | 1.1    | Introd  | luction                                                              | 1   |

|    | 1.2    | Thin-   | film solar cells                                                     | 2   |

|    |        | 1.2.1   | Limits and potential of thin-film silicon solar cells                | 2   |

|    |        | 1.2.2   | Light-trapping in solar cells                                        | 4   |

|    |        | 1.2.3   | Surface quality: critical parameters                                 |     |

|    | 1.3    | Passiv  | vation of thin silicon                                               | 7   |

|    |        | 1.3.1   | Silicon Dioxide                                                      | 8   |

|    |        | 1.3.2   | Silicon nitride                                                      |     |

|    |        | 1.3.3   | Alumina + annealing                                                  | 9   |

|    |        | 1.3.4   | Titanium Dioxide                                                     | 10  |

|    |        | 1.3.5   | Combinations: multi-layer passivation                                | 10  |

|    |        | 1.3.6   | Passivation and solar cell performance                               | 11  |

|    | 1.4    | Chara   | cterization of thin silicon                                          | 12  |

|    |        | 1.4.1   | Capacitance methods: MOS devices                                     |     |

|    |        | 1.4.2   | Photoluminescence                                                    |     |

| 2  | Fab    | ricatio | n                                                                    | 17  |

|    | 2.1    | Fabric  | eation of HUD thin silicon solar cells                               | 17  |

|    |        | 2.1.1   | Bonding and debonding of thin-Si wafers                              | 17  |

|    |        | 2.1.2   | Imprinting: SCIL                                                     | 19  |

|    | 2.2    | Passiv  | vation Techniques                                                    | 20  |

|    |        | 2.2.1   | Deposition of amorphous Al <sub>2</sub> O <sub>3</sub> and annealing | 20  |

|    |        | 2.2.2   | Deposition of amorphous SiO <sub>2</sub>                             | 21  |

|    |        | 2.2.3   | Deposition of $SiN_x$                                                | 21  |

| 3  | Cha    | racteri | ization                                                              | 23  |

|    | 3.1    | Evalua  | ation of optical properties with UV-VIS spectroscopy                 | 23  |

|    |        | 3 1 1   | Transmission measurement                                             | 23  |

|    |        | 3.1.2    | Reflection measurement                                           | 24 |

|----|--------|----------|------------------------------------------------------------------|----|

|    |        | 3.1.3    | Comparison with analytical results                               | 25 |

|    | 3.2    | EIS and  | d CV                                                             | 26 |

|    |        | 3.2.1    | Setup and measurement technique                                  | 26 |

|    |        | 3.2.2    | Analysis of the data                                             | 27 |

|    | 3.3    | Measu    | rement of Interface Traps in silicon using MOS capacitors: the   |    |

|    |        | Terma    | n method                                                         | 27 |

|    |        | 3.3.1    | Ideal $\Psi_S$ vs. V curves for the high-frequency Terman method | 29 |

|    | 3.4    | Lifetin  | nes measurements                                                 | 30 |

| 4  | Resi   | ults & D | Discussion                                                       | 33 |

|    | 4.1    | Fabrica  | ation of the samples                                             | 33 |

|    |        | 4.1.1    | SCIL fabrication and etch parameters                             | 33 |

|    |        | 4.1.2    | Passivation of the samples                                       | 33 |

|    | 4.2    | Optica   | l properties and absorption measurements                         | 34 |

|    | 4.3    | Surface  | e state density measurements                                     | 38 |

|    | 4.4    | Minori   | ty carrier lifetimes measurement                                 | 41 |

|    | 4.5    | Terma    | n method and NextNano                                            | 44 |

| 5  | Con    | clusion  | s & Outlook                                                      | 47 |

| 6  | Арр    | endix    |                                                                  | 49 |

| Bi | bliog  | raphy    |                                                                  | 55 |

| D€ | eclara | ation of | Authorship                                                       | 59 |

Introduction

#### 1.1 Introduction

Electricity provided by renewable technologies increased by 6% in 2019 alone and the energy from wind and solar each accounted for one third of the rise. That year renewable power represented 27% of the global electricity supply, with an increasing tendency. Nonetheless, as the new IPCC 2021 report pinpoints clearly, emissions need to be drastically reduced, putting as well more pressure on renewable energies. This sector needs to keep growing annually by at least 7% over the next ten years. By then the solar energy sector alone is envisioned to represent 21.8% of the total global renewable power [18]. This needs to go hand in hand with a renewable energy cost reduction. For moderate radiation areas the cost of PV energy is expected to achieve of fossil fuel by 2028 and 2046 for residential and industrial applications, respectively [15]. This forecast can only be met if efficiencies are further increased and costs reduced.

Solar cells based on single-junction monocrystalline semiconductors have almost reached the Shockley-Queisser (SQ) limit. This is the theoretical maximum light to electric power conversion efficiency of an ideal solar cell under a certain illumination spectrum [35]. Efficiencies of 25% and 20% have been reached for mono- and polycrystalline silicon cells, respectively [15]. These cells are based on the principle of single-pass photons, where incident photons need to be absorbed as efficiently as possible through rather thick absorbers [26]. To overcome the SQ limit and reduce costs, new light trapping and interference strategies are being developed in order to increase the effective path length of the photons, while slimming down simultaneously the absorber layer, but maintaining or even increasing the performance [26].

Crystalline silicon based solar cells represented 90% of the global photovoltaics market over the recent years. The silicon absorber layer alone accounts for about 40% of the final PV cost and reducing it's thickness is paramount for cost reduction [39], one of the many benefits of (ultra)thin-Si solar cells. Thinner cells require as well shorter deposition/growth times during production and the use of novel low-cost technologies like chemical vapor deposition may become possible for thin-Si solar cells [26]. In thin absorbers many limitations of bulk semiconductors can be avoided and the efficiency increased. Concerned are namely limitations dominated by recombination processes. In an ideal solar cell (SQ limit), the only recombination mechanism is radiative recombination, excluding the dominant bulk processes which can be limited by thin layers. Aiming for thinner layers paves the path to lighter, mechanically flexible and transparent applications,

#### Chapter 1

opening a new dimension of applications for solar cells [26, 40].

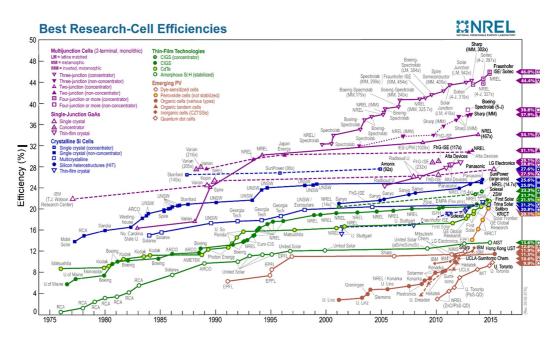

In Figure 1.1 the development of cell-efficiencies is depicted since 1975. Where the crystalline Si Cells have been plateauing since 2000, thin-film technologies, as well as multi-junction cells and new (emerging) technologies, have been continuously increasing. The trend is clear; Improved and new solar conversion technologies are on the rise.

**Figure 1.1:** Solar cell efficiencies per category since 1975, *courtesy of the National Renewable Energy Laboratory, Golden* [29]. Pink: Multi-junction cells, blue: C-Si cells, green: thin-film technologies, brown: emerging PVs.

#### 1.2 Thin-film solar cells

#### 1.2.1 Limits and potential of thin-film silicon solar cells

The SQ limit for a single junction c-Si cell under one sun and at room temperature is of 32.23% [15]. Incomplete absorption of incoming photons and non-radiative recombination of parasitic photogenerated charge carriers (parasitic absorption) make it impossible to reach the limit. As silicon has an indirect band gap, radiation in the range of 800-1100 nm is rather badly absorbed. Richter *et al.* (2013) suggested that the real efficiency limit in practice for an undoped c-Si absorber thickness of 110  $\mu$ m is 29.43% for perfect Lambertian light trapping [3, 34]. The absorption efficiency is strongly absorber thickness and wavelength dependent. For 2  $\mu$ m c-Si and in single-pass configuration, only 40% of the

photons with wavelengths above 650 nm are absorbed [26]. Improving the absorption close to the bandgap of 1100 nm is thus crucial in order to further push the absorption efficiency.

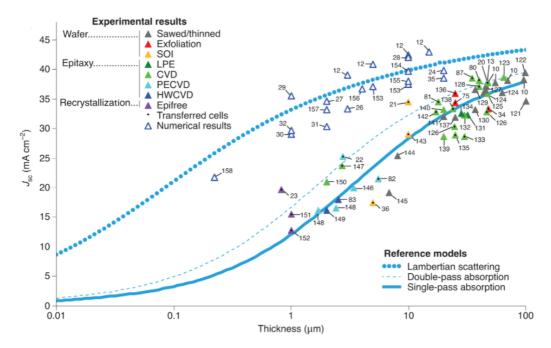

Bhattacharya *et al.* (2019) suggest that by including wave-interference corrections in structures at the optical wavelength scale, thin-Si can overcome the theoretical efficiency limits of thick Si cells . The dwell time is much longer in thin-film cells, as wave interference reduces the group velocity [3]. Figure 1.2 shows experimental results for single-pass absorption (ultra-)thin c-Si solar cells and theoretical results based on absorption measurements for nanostructured front surfaces. They suggest that the Lambertian scattering limit can be exceeded by optimized surface structuring. Thinner solar cells have as well reduced electron collection paths which is a promising strategy to reduce bulk recombination and eventually even surface recombination, if the diffusion lengths of the minority charge carriers are larger than the mean path to the contacts [28]. By using IBC contacts, the path of the charge carriers generated at the surface could be short enough to overcome before (surface) recombination occurs.

**Figure 1.2:** Short-circuit current as a measure for the absorption efficiency as a function of the aborber thickness for different crystal growth methods. Filled triangles represent experimental results, empty triangles numerical results (based on absorption measurements). Cells with record efficiencies exceeding the Lambertian limit make use of nanostructured surfaces. *Courtesy of Massiot et al.* (2020) [26].

#### 1.2.2 Light-trapping in solar cells

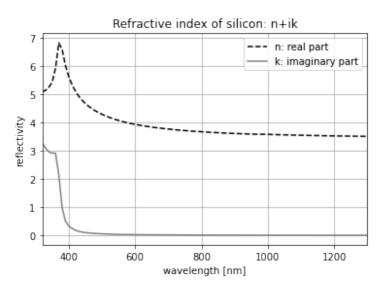

The absorption coefficient of the semiconductor depends on intrinsic properties like the complex refractive index and the sheet thickness. The refractive index of silicon is strongly wavelength dependent (appendix, Figure 6.1) and thus is as well the absorption efficiency. The absorption as a function of wavelength is expressed as:  $A(\lambda) = 1 - e^{\alpha d}$  or  $A(\lambda) = 1 - e^{F\alpha d}$ , with  $\alpha = 4\pi\kappa/\lambda$  the absorption coefficient and F the optical path enhancement factor, describing the efficiency of light trapping, increased by resonance for instance [26]. The optical path increase is maximized if the photons are scattered fully randomly upon incidence and internally. This can theoretically be achieved with a back mirror, perfect anti-reflective coating (ARC) and a Lambertian scatterer.

There's thus a big potential to be explored in new light-trapping technologies for ultrathin solar cells by patterning the surface at the nanometer scale. Nanopatterning increases not only the absorption of light, but decreases as well the surface reflectance [28]. With Lambertian light trapping, the currently achieved efficiency of 26% for c-Si solar cells could be obtained with 10  $\mu$ m c-Si absorbers [26]. Structures resulting in multi-resonant absorption (slow photonic modes) have shown to reach or even exceed the theoretical Lambertian limit over the broad solar spectrum, where F reached almost maximal enhancement [3, 26]. These technologies are typically the ones shown in Figure 1.2.

Thinning down the absorber comes along with new challenges in the solar cell architecture. Texturing may increase the non-radiative surface recombination or parasitic absorption might occur in contact layers. Selective contacting, ARC and surface passivation may be even important in ultrathin solar cells [26]. Unless, the charge carriers can be collected before recombination due to short distances that need to be overcome till the contacts.

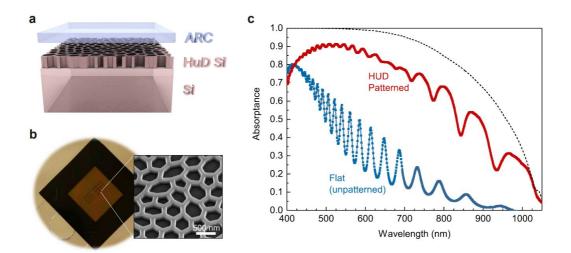

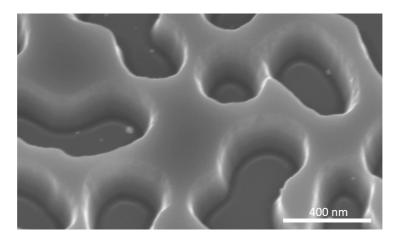

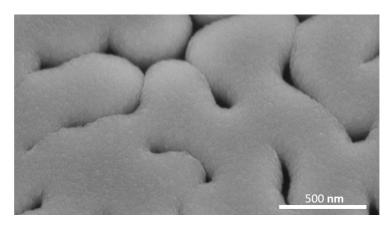

Hyper-uniform disordered (HUD) thin-Si solar cells HUD structures are a type of nanotexturing that couple light efficiently into silicon slab optical modes. Over a larger scale, these structures are statistically isotropic and thus not completely random. In terms of density distribution, HUD structures are more similar to ordered solids than amorphous materials. This large-scale isotropy can be applied to photonic materials in order to design properties with well defined photonic gaps that allow modes to propagate through the structure. Ultimately, this allows the a exact control of light transport and optical properties [40]. Tavakoli *et al.* (2020) reported from analytical results that efficiencies above 20% could be reached with a 1  $\mu$ m HUD structured c-Si absorbers. This is shown in Figure 1.3, c), where the absorbtance approaches the Lambertian limit. The theoretical absorbtance of the 200 nm deep HUD structures on 1  $\mu$ m c-Si is suggested to well outperform the flat 1  $\mu$ m c-Si. The dashed line represents the Lambertian limit for 1  $\mu$ m c-Si. On Figure 1.3, b) a SEM image of a honeycomb HUD structure is shown and in a) the HUD on top of a thicker c-Si substrate [40].

**Figure 1.3:** a) 200 nm HUD texturing on top of a 1  $\mu$ m Si substrate, covered by an polymeric ARC. b) SEM picture of an optimized honeycomb-like HUD texture. c) Absorptance spectrum of the structure contrasted to flat 1  $\mu$ m Si, where the dashed line corresponds to the Lambertian limit for the silicon of the same thickness. *Courtesy of Tavakoli et al.* (2020) [20].

The refractive index of the HUD pattern can be approximated by:

$$n_{HUD} \approx n_{Si} \cdot ff + n_{LRM}(1 - ff) \tag{1.1}$$

where ff is the filling fraction of the pattern,  $n_{Si}$  the refractive index of the silicon substrate and  $n_{LRM}$  the refractive index of the (polymeric) coating that is filling up the free space. For free standing patterns the latter would be the refractive index of air. The main effect of nanostructuring is increased light trapping and but as well increased charge recombination by high surface-volume ratios [40].

#### 1.2.3 Surface quality: critical parameters

Micro- and nanostructured c-Si solar cells still haven't reached as high efficiencies as thick absorber cells. This is mainly due to much higher surface recombination velocities originating in the high aspect ratio features and surface-to-volume ratios. Important parameters to estimate properties of the surface are surface recombination velocity, minority charge carrier lifetime and interface trap density [28].

The effective carrier lifetime is the ratio between the excess minority carrier density  $(\Delta p)$  and the effective recombination rate  $(U_{eff})$ :  $\tau_{eff} := \Delta p/U_{eff}$ . The effective recombination rate is the sum of all the mechanisms contributing to recombination. When the surface

and bulk mechanisms are considered, the effective carrier lifetime becomes [11]:

$$\frac{1}{\tau_{eff}} = \frac{1}{\tau_{bulk}} + \frac{1}{\tau_s} \tag{1.2}$$

The recombination lifetime describes the process of a charge in an excited state (in a space-charge region) returning to equilibrium. The lifetimes can be correlated to interface trap state densities, changing the dynamics of charging/decharging. Recombination taking place at the surface is characterized by the surface recombination velocity  $(S_r)$ . Simultaneously, recombination in the bulk occurs and it is difficult to separate their contributions [37]. In ultrathin Si the effective lifetimes measured are dominated by surface recombination.

If the bulk lifetimes are assumed infinite, the maximal effective surface recombination can be expressed as :  $S_r^{max} \leq \frac{W}{2 \cdot \tau_{eff}}$ , where W the substrate thickness [17].

When silicon is covered by a dielectric, a major discontinuity is introduced between the crystalline semiconductor surface and adjacent layer. This results in an interface trap density  $(D_{it})$  and trapped oxide charges  $(Q_{it})$ , introduced for example by impurities, excess silicon (trivalent) or contrarily dangling Si bonds (broken Si-H bonds). These interface traps are introducing energy levels into the former state-free bandgap of Si. By means of these intermediate energy levels, charges can be exchanged very quickly with the silicon and thus influence its properties. Whereas  $D_{it}$  is produced by the crystalline discontinuity at the surface,  $Q_{it}$  vary with the occupancy of the Fermi level, i.e the applied voltage. The Fermi level changes with respect to the surface trap energies, modifying the charges and the effective surface capacitance. Another type of charges are fixed oxide charges  $(Q_f)$ , which are situated near or at the interface and are not influenced when a voltage is applied [38, 41].

First, the density of interface traps with respect to the location in the band gap and second, the relaxation time of the charges occupying these states, i.e the lifetime [41], are two important parameters in order to quantify and understand the interface traps.

Independently of the nature of the semiconductor, both donor and acceptor interface trap states coexist. Therefore, an equivalent  $D_{it}$  distribution is used with respect to a neutral level  $E_0$ . Above this level the states are of acceptor, below of donor type. In order to determine  $D_{it}$  experimentally, the change of  $Q_{it}$  when varying  $E_F$  or the surface potential  $\Psi_S$  can be measured. The surface trap states are distributed over the band gap and can be described by a density distribution function [38]:

$$D_{it} = \frac{1}{q} \frac{dQ_{it}}{dE} \quad [\#traps/cm^2 eV]$$

(1.3)

#### 1.3 Passivation of thin silicon

With advancing technology the bulk carrier lifetimes in c-Si have been increasing, making the surface recombination and at the contacts one of the main drawbacks of the current c-Si cells. The surface recombination is not only relatively more important in thin-Si than in bulk Si, but gets even more important in nanostructured surfaces with high surface-to-volume ratios.

The minority carrier lifetimes can be increased by two approaches. The first is based on the reduction of the interface trap state density, the second reduces the electron (n-doped) or hole (p-doped) concentration at the surface in order decrease the probability of recombination. The former approach is called chemical passivation, the latter field-effect passivation and can be used combined, too [17].

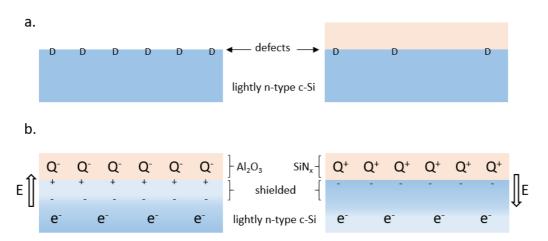

**Figure 1.4:** Passivation schemes for n-type c-Si. a) Chemical passivation in order to decrease the number of defects (D) at the semiconductor surface. b) Field-effect passivation by adding negative fixed-charges ( $Q^-$ ) or positive fixed-charges ( $Q^+$ ) to the semiconductor surface. The electrical field can be strong enough to shield the surface from either electrons (left) or holes (right) for lightly n-doped c-Si.

**Chemical passivation** In order to reduce the number of defects at the surface, chemical passivation can be used to diminish the effect or amount of impurities, trivalent silicon or dangling Si bonds. So can unsaturated Si bonds be stabilized by atomic hydrogen [17]. This is illustrated in Figure 1.4 a, where the defect density (D) is reduced after the application of a passivation layer.

#### **Chapter 1** Introduction

**Field-effect passivation** In order to reduce the probability of recombination at the surface, an electrical field can be applied beneath the silicon surface in order to lower the concentration of holes or electrons at the surface. The minority carrier concentration is directly correlated to the surface recombination velocity [17]. This is depicted in Figure 1.4 b, where either the surface is either shielded from electrons (left) or holes (right), depending on the fixed-charges applied at the surface. In the absence of an additional field, holes are the minority carriers in n-doped, electrons in p-doped. Under strong positive-charge density, holes become the minority charge carriers at the surface for lightly n- and p-doped c-Si. On the contrary, a strong negative-charge density proved to shield the surface efficiently for lightly n- and p-type c-Si as well, hence when the electrons are the minority charge carriers. This is shown in Figure 1.4 b, left, where the electrons added by doping (e<sup>-</sup>) are still pushed back from the surface. Therefore, efficient field-effect passivation can be obtained by shielding the surface from either electrons or holes, if the fixed-charge density is sufficiently high [17].

#### 1.3.1 Silicon Dioxide

Thermally grown  $SiO_2$  is one of the main industrial approaches to reduce surface recombination velocities. The interface between the silicon dioxide and the silicon is of very good quality, effectively reducing defects at the silicon surface. Further improvements have been reported after annealing in a  $H_2$  atmosphere, called hydrogenation or *alnealing* [9, 17]. Due to high processing temperatures that make the deposition inefficient at industrial scale and require low impurity densities in order to avoid bulk degradation, the thermally grown  $SiO_2$  has been largely replaced by PECVD grown layers.

Furthermore, apart from the good chemical passivation properties,  $SiO_2$  has a high positive fixed-charge density and contributes thus as well by field-effect passivation. Zhang *et al.* (2017) did an extensive study on the impact of hydrogen and oxygen incorporation in to the a- $SiO_x$ . The surface passivation is known to be very good, but important parasitic absorption losses have been observed. Hence, an approach that includes more oxygen into the oxide has been studied lately, in order to reduce the parasitic absorption. Oxygen has a bandgap widening effect on the silicon. They conclude that: "A compact, less-defective and ordered microstructure of the a-SiOx:H film can only be obtained when there comes a trade-off between Si-O and Si-H(Si<sub>3</sub>) bonding formation." Controlling the exact composition and adding eventual annealing steps in oxygen or hydrogen atmospheres can be used to further improve the surface passivation quality [43].

#### 1.3.2 Silicon nitride

$SiN_x$  is a standardized approach for surface passivation. Due to high positive fixed charge densities induced in a- $SiN_x$ :H layers, the hole concentration is reduced at the surface [17]. This makes it very efficient for n-doped c-Si. For the reason explained above, a high

surface passivation can be achieved as well on lightly p-doped c-Si.

For both,  $SiN_x$  and  $SiO_2$  a dependence of the effective lifetimes and the injection depth has been observed. The effective lifetimes decrease at high injection levels for thick c-Si because the recombination is dominated in the bulk. Some decrease in lifetimes at lower injection levels has been explained to be related to bulk recombination in the depletion region (when the surface is shielded from electrons) [17].

#### 1.3.3 Alumina + annealing

Hoex *et al.* (2008) reported that ALD deposited alumina as passivation performed similarly as high-temperature thermal SiO<sub>2</sub> on lightly n-doped c-Si. This means that the negative fixed charge provided by alumina shields the surface efficiently for lightly n-doped Si, too, and should passivate the surface of c-Si [17]. Alumina provides as well good chemical passivation due to low interface defect density when deposited on c-Si [19]. Further, Hoex *et al.* (2008) studied the lifetimes in c-Si by adding positive corona charges on the surface of the alumina in order to compensate the negative fixed charges in the passivation layer. The lifetimes in c-Si showed to decrease very fast with increasing corona charge density at the surface (hence cancelling out the field-effect passivation effect). By identifying the point of minimal lifetimes, the negative fixed charge density ( $Q_f$ ) in an 26 nm Al<sub>2</sub>O<sub>3</sub> layer was estimated to be 1.3·10<sup>13</sup> cm<sup>-2</sup>. Additionally, they found that the recombination rate is proportional to  $1/Q_f^2$  for lightly doped c-Si, independent of the positive or negative fixed charge density and could deduce that the tested 26 nm Al<sub>2</sub>O<sub>3</sub> layer is 2 and 4 orders of magnitude more efficient than a standard *a*-SiN<sub>x</sub>:H ( $Q_f = 10^{12}$  cm<sup>-2</sup>) and thermal SiO<sub>2</sub> ( $Q_f = 10^{12}$  cm<sup>-2</sup>) layer, respectively [17].

The passivation efficiency depends strongly on the injection level. Apart from the decrease in effective lifetimes at high injection levels, they decrease as well slightly at low levels. This is explained by bulk recombination losses in the shielded (electron depleted) close to the Si surface. Nevertheless, effective lifetimes exceeding 18 ms have been measured by QSSPL for flat lightly n-doped low-resistivity c-Si wafers passivated by 30 nm  $Al_2O_3$  [17]. A standard RCA1 and RCA 2 clean and a dip into diluted 1% HF prior to deposition is commonly done in order to leaving behind a H-terminated, hydrophobic c-Si surface [17, 19].

The influence of annealing on the surface passivation properties of  $Al_2O_3$  was extensively reported by Kersten *et al.* (2013). The interface trap density was affected by both, the annealing temperature and atmosphere. The fixed charge density on the contrary was influenced solemnly by the annealing temperature [19]. The best results were reported for low injection level c-Si at an annealing temperature of 470 °C,  $O_2$  atmosphere and 10 min. Temperatures above 400 °C yielded very good results for high injection levels [19]. Hoex *et al.* (2008) did an annealing process at 425 °C for 30 min in  $N_2$  atmosphere.

#### 1.3.4 Titanium Dioxide

Interesting c-Si passivation results have been reported using TiO<sub>2</sub>. Ho *et al.* (2015) reported the improvement of the conversion efficiency of c-Si thin-solar cell with a nanotextured surface from 8.13 to 9.62% after the passivation with 15 nm of TiO<sub>2</sub> and 10 min annealing at  $300^{\circ}$ C in N<sub>2</sub> atmosphere. The Si absorber thickness was about 5.87  $\mu$ m and a texture depth of 400 nm. They report a effective reduction of surface recombination after the passivation [16]. This effect is among other thanks to its appropriate band offset when in contact with c-Si, namely a small conduction, and large valence band off-set [24]. A interfacial SiO<sub>2</sub> layer and Si-O-Ti bonds have been identified as the main chemical passivation effects [24]. Effective minority carrier lifetimes of up to 500  $\mu$ s or even 1500  $\mu$ s have been reported for low resistivity n-c-FZ-Si with only a couple of nm's of oxide. Layers thicker than 6 nm have shown to have the adversary effect due to stress-related phase transitions within the oxide layer. A common way of deposition is by ALD [24].

#### 1.3.5 Combinations: multi-layer passivation

Tan *et al.* (2017) reported a very efficient double-layer passivation on pyramidal 20  $\mu$ m thin-Si with a feature size of 3-10  $\mu$ m, using a combination of  $Al_2O_3$  and  $SiN_x$ . They contrast single-layer passivation consisting of 80 nm PECVD deposited  $SiN_x$  to double-layer passivation of 3 nm ALD deposited  $Al_2O_3$  followed by 80 nm of PECVD deposited  $SiN_x$ . Comparing planar to textured Si solar cells passivated with  $SiN_x$  only, the efficiency increases by 4.5% to 15.1% for textured one. By adding the second passivation layer, the efficiency was further increased by 1.3%, improving both the short-circuit current density and the open-circuit voltage [39].

Schmidt *et al.* (2008) compared passivation with  $SiO_2$ ,  $Al_2O_3$  and a combination of both. The surface recombination velocities of 130 nm of  $Al_2O_3$  and a stack of  $Al_2O_3/SiO_2$  30/200 nm were comparable and even inferior to alnealed  $SiO_2$  [36]. This is attributed to the hydrogenation of the interface states during the silicon oxide deposition [36].

Mallorquí *et al.* (2015) compared the before mentioned approaches on pn-junction nanowire array c-Si solar cells. Similar  $V_{oc}$  and  $J_{sc}$  have been achieved for  $SiN_x$  and  $Al_2O_3$  passivated devices, resulting in efficiencies of 3.4% and 2.4%, respectively. Surprisingly, the thermally grown  $SiO_2$  that is known for high chemical passivation and good surface recombination reduction, performed very poorly with a efficiency of only 1.2%. When a 19 nm layer of  $SiN_x$  was deposited on top of the  $SiO_2$ , the properties were greatly enhanced to an efficiency of 9.9% [25].

The excellent chemical passivation properties of SiO<sub>2</sub> have been reported to further be enhanced by depositing a thin layer of Al and annealing prior to the oxide deposition. This adds positive fixed charges at the surface, providing a field-effect passivation by

keeping holes away from the surface [17]. The best surface passivation should thus be achieved for high fixed charge density and low interface trap density.

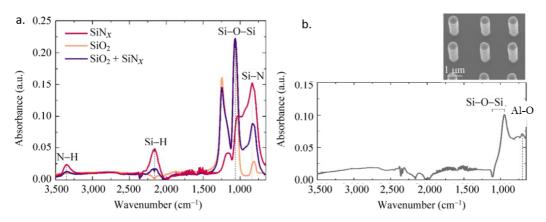

Mallorquí *et al.* (2015) investigated the interface between silicon and its passivation layer. Their results are shown in Figure 1.5. The peak denoted as Si-H for the  $SiN_x$  passivating layer was separated into six peaks representing: (1) H-Si-Si<sub>3</sub>, (2) H-Si-HSi<sub>2</sub>, (3) H-Si-NSi<sub>2</sub>, (4) H-Si-SiN<sub>2</sub>/H-Si-SiNH, (5) H-Si-HN<sub>2</sub> and (6) H-Si-N<sub>3</sub>. N-H bonds are related to the formation of trivalent silicon ( $\cdot$ Si $\equiv$ Si<sub>3</sub>) dangling bonds which results in a fixed positive charge density [25].

The high chemical passivation is related to the low interface defect density. The only major defect in the  $\mathrm{Si/SiO_3}$  interface is the Si atom with a dangling bond due to a lattice mismatch and leads to a fixed positive charge. A hydrogen treatment is usually done for its passivation [25]. In the double layer appears hence the Si-H peak, being the hydrogen passivated dangling Si bond. Furthermore, the  $\mathrm{SiO_2}$  interlayer removes significantly Si-N bonds. Consequently the field-effect passivation contribution by the  $\mathrm{SiO_2/SiN_x}$  double-layer is reduced [25].

As for  $Al_2O_3$ , apart from the Al-O peak, there's the broad Si-O-Si signal due to a thin interlayer of  $SiO_x$  formed before ALD [17]. This interlayer could be beneficial by adding a high density of Al vacancies, which can, like interstitial oxygen, be charged negatively and resulting in fixed negative charges [25].

**Figure 1.5:** FTIR spectra of the interfaces between passivation layers and silicon in a nanowire array. a)  $Si/SiO_x$ ,  $Si/SiO_x$ ,  $Si/SiO_x$ + $SiN_x$ . b)  $Si/Al_2O_3$  adapted from Mallorquí et al. (2015) [25].

#### 1.3.6 Passivation and solar cell performance

Whereas low surface recombination velocities and high minority carrier lifetimes are good indicators for efficient charge generation and dynamics at the surface, they do not imply better solar cell performance [25]. This might become particularly true for nanopatterned

#### **Chapter 1** Introduction

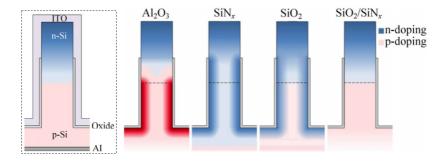

solar cells, as observed by Mallorquí *et al.* (2015) for arrays of nanowires (NWs). The above mentioned oddity of  $SiO_2$  leading to a good chemical passivation, nevertheless performing badly in solar conversion, is related to he high aspect ratios of the structure. In the case of a positive fixed charge, electrons are attracted towards the surface and holes are forced towards the core of the NW. In low p-doped regions of the Si NWs, holes become minority carriers and the pn-junction is moved to the base of the NWs for high positive fixed charge densities. This is illustrated in Figure 1.6. For low positive fixed charges, no inversions happens in flat Si. In NWs however, inversion can occur directly at the surface, leading to an annihilation of hole and electron densities somewhere in the core. In this region of similar densities, significant recombination occurs and the properties degrade [25]. Generally, inversion occurs when the charge in the passivating layer is higher than what the ionized dopants in the depletion layer can balance [9]. For  $Si/SiN_x$  the junction is pushed to the base of the NWs, decreasing the surface recombination. With  $Si/Al_2O_3$  passivation inversion occurs in the NWs due to the very specific pn-junction position of their architecture.

In conclusion, when using high aspect ratio structures, the passivation can result in opposite results due to the small dimensions, as the depletion layers might come close to the feature size.

**Figure 1.6:** Illustration of the carrier density profile in the NW of a solar cell based on high aspect ratio NW arrays by Mallorquí *et al.* (2015). Depending on the passivation materials, the pn-junction (dashed line: initial position) is moved and inversion regions with increased recombination might occur [25].

#### 1.4 Characterization of thin silicon

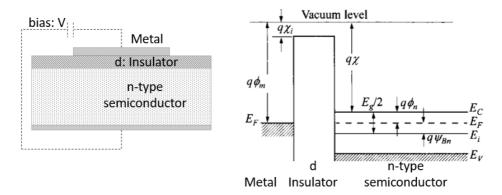

#### 1.4.1 Capacitance methods: MOS devices

The surface physics of silicon can be studied by means of metal-oxide-silicon (MOS) structures, as shown in Figure 1.7, left. This method gives access to the capacitance of the layers which are a good mean to characterize the semiconductor/oxide interface trap

density distribution [28]. One quantification approach of the interface trap density is based on the the comparison of the ideal C-V graph with the measured C-V curves (i.e *non ideal*). This is called the Terman method, using the full interface state method [28, 31, 38, 41].

**Figure 1.7:** Scheme of a typical metal-insulator-semiconductor (MIS) capacitor (left) with energy band diagram without applied bias at equilibrium (V=0) (right). *Courtesy of Sze et al.* [38].

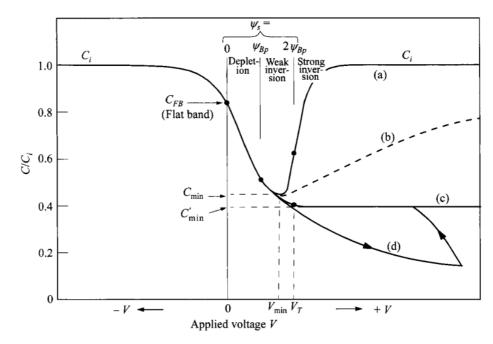

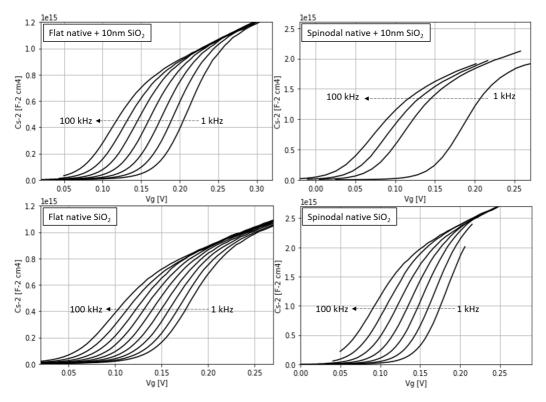

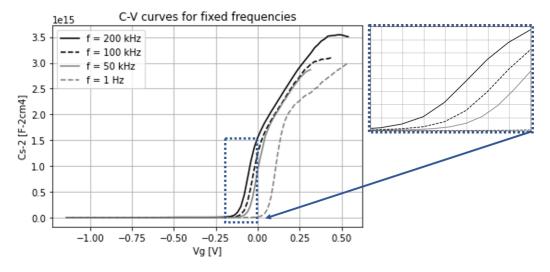

As can be seen on Figure 1.7, left, the contacting of the surface is necessary and is done by metallic contacts (solid-state contacts) on flat MOS systems. However, on high aspect ratio structures this is very tedious and imprecise which makes many characterization methods unsuitable for nanostructured materials. The use of electrochemical impedance spectroscopy (EIS) to obtain the interface trap densities has been used widely for such materials. This method replaces the solid-state contacts with a highly conductive electrolyte, which makes conformal electrical contact [27, 28]. The capacitance of the MOS device changes depending on the applied DC voltage and is frequency dependent, as shown in Figure 1.8. The electrolyte of high ion concentration blocks efficiently the semiconductor.

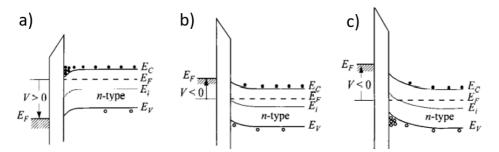

**Basic relations** As illustrated in Figure 1.9, under applied bias, three regimes can be distinguished at a n-type semiconductor surface. (i) *accumulation* for V>0: close to the surface the conduction-band edge  $E_C$  bends downward, approaching the Fermi level and as the carrier density depends exponentially on  $\Delta E = E_C - E_F$ , electrons accumulate locally. (ii) *depletion* for V<0: the bands bend upward under depletion of the majority carriers. (iii) inversion under V $\ll$ 0: the bands bend stronger. As the intrinsic level crosses over the Fermi level, locally the number of minority (holes) is larger than the number of majority charge carriers. As an ideal MOS structure is considered, no Fermi-level bending occurs and no current flows and  $dE_F/dx = 0$ . When the DC voltage is swept with a certain frequency, then the semiconductor undergoes inversion, depletion, and accumulation

#### **Chapter 1** Introduction

**Figure 1.8:** C-V curve of a MOS structure undergoing inversion, depletion and accumulation for a) low frequency (quadsistatic), b) intermediate frequency, c) high frequency [38].

with increasing voltage (versus reference electrode), as shown in Figure 1.8. For the low frequency case, the capacitance increases anew as a thin inversion layer forms at the interface [28, 38].

The semiconductor surface potential is defined as  $\Psi_S \equiv \Psi_n(x \to 0)$  with respect to the bulk  $(x = \infty)$  with:

$$\Psi_n(x) \equiv \frac{E_i(x) - E_i(\infty)}{q} \tag{1.4}$$

The Fermi-level is in flat-band condition, if V=0 where  $\Psi_S=0$ . Depletion occurs when  $\Psi_S\in [\Psi_{Bn},0]$ , weak inversion when  $\Psi_S=\Psi_{Bn}$  and strong inversion when  $\Psi_S=2\Psi_{Bn}$ . If  $C_D$  is the semiconductor depletion layer capacitance, then the total capacitance can be expressed as the two in series:

$$C = \frac{C_i C_D}{C_i + C_D} \tag{1.5}$$

Where  $C_i$  is constant for a certain thickness,  $C_D$  depends both on the net charge distribution on the semiconductor surface, i.e the surface voltage  $\Psi_S$  and voltage drop, and the measurement frequency. It can be expressed as  $C_D \equiv dQ_S/d\Psi_S$  (differentiating the excess surface charge with respect to the surface potential) [38, 41]. The capacitance and the

**Figure 1.9:** Band diagram for ideal MIS capacitors with a n-type semiconductor in different regimes: a) accumulation for V>0, b) depletion for V < 0, c) inversion for V $\ll$ 0 [38].

density of interface traps are related as [31]:

$$C_{it} \equiv \frac{dQ_{it}}{d\Psi_S} = q^2 D_{it} \tag{1.6}$$

As the voltage increases, both, the depletion width  $W_D$  and the surface potential  $\Psi_S$ , increase. The depletion width reaches a maximum when the strong inversion regime is reached at  $\Psi_S = 2\Psi_{Bn}$  [31].

**Electrolyte-semiconductor surface dynamics** When an electrolyte is in contact with a semiconductor, the redox potential in the electrolyte and the Fermi energy in the semiconductor align via band bending. For an n-type semiconductor with  $E_F > E_{redox}$ , electrons are released from the semiconductor to the solution. The electron depleted region of the semiconductor is called space charge (SC) layer within which the bands are bent upwards to equilibrium with the increased  $E_{redox}$ . In the electrolyte this charged region is denoted the Helmholtz layer [45].

Energy states closest to the surface are able to transfer charges between the electrolyte and the semiconductor. If a voltage is applied, then all the layers contribute:  $\Delta V = \Delta V_{SC} + \Delta V_{H}$  and the neutrality among exchanged charges requires:  $Q_{solution} = Q_{SC} + Q_{SS}$ . The total capacitance of the interface can be expressed as:

$$\frac{1}{C_{tot}} = \frac{1}{C_{sc} + C_{ss}} + \frac{1}{C_H} \tag{1.7}$$

As applied by Meng (2017) and Mikulik (2018) *et al.*, the circuit of a MOS capacitor with a electrolyte replacing the metal gate simplifies to the solid-state case. The electrical double layer capacitance is typically 10x greater than the oxide capacitance in these setups and can be ignored [27, 28].

Hence, when looking at the dynamics between applied voltage and measured capacitance, information about the surface states (SS) can be extracted. For a semiconductor

#### **Chapter 1** Introduction

with a low density of surface states ( $C_H \gg C_{SC}$ ) and with  $E_{redox} \sim E_F$  (i.e  $C_{SS} \ll C_{SC}$ ), the Mott-Schottky equation is derived, relating the interface capacitance to the electrode potential [14, 44, 45]:

$$\frac{1}{C_{sc}^2} = \frac{2}{e\epsilon\epsilon_0 N_d} \cdot \left( (V_{applied} - V_{fb}) - \frac{k_B T}{e} \right)$$

(1.8)

By plotting  $1/C_{SC}^2$  vs. V and fitting a line to the linear part of the graph, the flat band potential can be extracted at its intersection with the V-axis and the slope gives the doping level  $N_d$  [12, 45]. The slope of the plateau is closely correlated to the density of surface states. The bigger the slope, the fewer surface states and the smaller the depletion region, and vice versa [45]. Hence this slope can be used for qualitative comparison of interface trap states between among different.

#### 1.4.2 Photoluminescence

With photoluminescence the near bandgap recombination radiation (photoluminescence) after photoexcitation is measured. The band-to-band PL signal gives fundamental information about the absorption coefficient, radiative recombination coefficient and the influence doping of the bandgap. Applied to photovoltaics, parameters like the diffusion length of minority carriers can be extracted or the light trapping efficiency of plasmonic structures can be evaluated [30]. Time-resolved (TRPL) or quasi-steady-state (QSSPL) photoluminescence are both non-destructive and very sensitive techniques, adapted to small and thin samples with the detection potential of low emission signals. In TRPL the excess minority-carrier concentration can be measured as a function of time and gives access to the transient decay of the photoluminescence signal, correlated to the minority-carrier density. The latter is dependent on both, the carrier lifetime and the diffusion rate and is thus structure dependent [2]. In QSSPL the radiative recombination of continuously generated excess charge carriers is measured.

For bulk silicon, the effective lifetime can be written as [2]:

$$\frac{1}{\tau_{PL}} = \frac{1}{\tau_B} + \frac{2S}{d} \tag{1.9}$$

With S the interface recombination velocity, d the active layer thickness and  $\tau_B$  the bulk lifetime.

#### 2.1 Fabrication of HUD thin silicon solar cells

The goal is to find a perfect passivation recipe on low n-doped CZ (001)-silicon wafers and to reproduce it on thinned-down solar cells. First, the effects of HUD nanostructures was to be studied on thick 500  $\mu$ m silicon. Then passivation layers of amorphous Al<sub>2</sub>O<sub>3</sub>, amorphous SiO<sub>2</sub>, amorphous Si<sub>2</sub>N<sub>3</sub> and combinations thereof were to be tested on these thick Si samples. The same recipes were to be then tested on diverse thin nanostructured silicon samples. Finally, the most promising procedures were to be repeated on thinned-down silicon solar cells. The materials used are 10  $\mu$ m (University Wafer), 20  $\mu$ m (provider not specified), 30  $\mu$ m (Virginia Wafers) and 500  $\mu$ m (Seifert Albert) moderately n-doped (10<sup>15</sup> cm<sup>-3</sup> CZ dsp (001)-silicon wafers and finally, approximately 50  $\mu$ m thin IBC Si-solar cells. Whereas the 10 and 30  $\mu$ m Si wafers were free-standing wafers of 1" diameter and needed to be bonded onto quartz substrates, the 20  $\mu$ m Si wafers were already bonded by PMMA onto 1 mm Si. As the backside of the thinned-down solar cells are protected by parylene, processing temperatures shouldn't exceed the degradation temperature of 250°C.

#### 2.1.1 Bonding and debonding of thin-Si wafers

During the handling of the thin-Si wafers, air flow needs to be taken into account. It is sufficient to make the wafers levitate and crash or bond statically somewhere. When the wafers are bonded only with water to the substrate, the static attraction to the wafer box was enough to lift the wafers from the substrate. To impede this, a piece of lens paper (Salm en Kipp BV) was used as a protection.

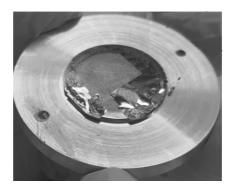

**1" thin-Si wafers** The 10 and 30  $\mu$ m silicon wafers are very fragile and they were bonded to a substrate before imprint. The mount of the spin-coater needs to be of perfect surface quality in order to reduce the risks of breakage. If PMMA flows between the holder and the wafer during the spin-coating, due to edge cracks for example, then the wafers are most likely to break upon removal of the holder and could stay sticking partially to the holder (Figure 2.1).

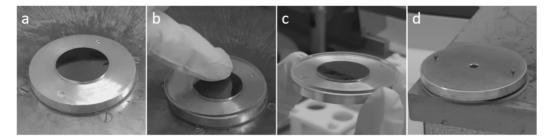

A 2" 1.5 mm thick quartz wafer was used as a carrier wafer. The procedure is shown in Figure 2.2. The Si wafer was hold by vacuum suction while 400 nm PMMA were

#### **Chapter 2** Fabrication

spin-coated on top. The carrier wafer was positioned gently and pressed lightly on the Si wafer. The whole stack is then transferred to a hot plate and cured at 120°C for 4 minutes. The difference in thermal expansion between both materials didn't induce any cracking and eventually even aided the detachment. The vacuum that held the carrier wafer to the mount should release automatically after maximally a couple of minutes. Alternatively, pressured nitrogen could be applied through the backside of the holder.

**Figure 2.1:** Incomplete debonding of a 30  $\mu$ m silicon wafer after an attempt to bond it to a carrier quartz wafer.

**Figure 2.2:** Bonding procedure for thin-Si wafers. a) Vacuum-bonded 30  $\mu$ m Si wafer on a customized mount. b) Bonding to a 1.5 mm thick quartz wafer after spin-coating of 400 nm PMMA. c) Transfer of the whole stack. d) Curing of the stack up-side down at 120°C for 4 minutes. The vacuum seal should release after a couple of minutes and the Si wafer remains bonded to the quartz.

Successively, in order to debond the wafer from the quartz, it was left to sit in an acetone bath for a couple of hours. Afterwards, by sliding it several times into water at a 45° angle with respect to the surface, it should float up onto the water surface at once.

**20**  $\mu$ m thin-Si wafers As the 20  $\mu$ m were already bonded by PMMA to 1 mm Si, the full stack could be cleaved in custom sized pieces. To do so, the wafers were nudged deeply thin-Si on top. This yielded better edge quality than having the thin-Si on the

bottom. Micro cracks were easily induced at the edges, making the wafer more prone to breakage or loosing small debris. The samples were imprinted in the bonded state. For debonding, an acetone bath was used again. However, as the substrate (thick Si) didn't have any excess area under the thin-Si, it couldn't be grabbed with a pair of tweezers and repetitively immersed in water until flotation. Hence, the debonding was done manually immersed in water. The sample spent 24h upside-up in an acetone bath, dissolving the PMMA. Then, the thin wafer was guided gently with a pair of tweezers onto the immersed future substrate. The latter could afterwards be lifted and as the water evaporated, the 20  $\mu$ m wafer remained bonded. A faster method is debonding my thermal expansion. Some of bonded samples have as well been passivated directly in order to see if the conformally deposited oxide would hinder the debonding by acetone. This showed that by putting the stack on a 250 °C hotplate didn't induce any cracks but smoothly debonded the thin-Si within a couple of seconds instead. This however doesn't dissolve and remove the residual PMMA.

#### 2.1.2 Imprinting: SCIL

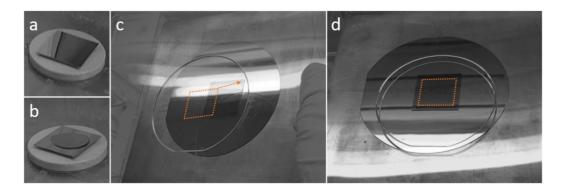

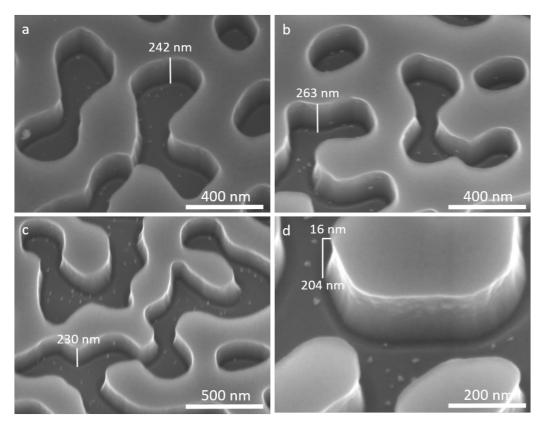

The method presented has been developed under tedious analysis and step-by-step adaptation of the process by a previous group member. The final SCIL procedure is shown in Figure 2.3. First, 250 nm solgel are spin-coated on the vacuum held sample. Then it was transferred to a support that would allow free gliding (fixed and polished 4" Si wafer). The stamp was placed carefully, well-oriented on the sample and pressure was applied with a rolling motion of the thumb. After 9 minutes of evaporation time, the stack was turned upside-down and the stamp was bent slightly until all the edges were detached. The sample was removed at once with a pair of tweezers. The stamp was rinsed after each use consecutively with water-ethanol-water and nitrogen dried. If small debris remained stuck to the stamp, another mock stamping cycle can be done to remove it.

The stamped sample underwent three etching steps, using the Oxford 100 Cobra system. First, the solgel and the PMMA were etched with a 120 s CHF $_3$  step at 20°C, preceded by a O $_2$  plasma clean. Afterwards, the system was heated up to 60°C and the native oxide was etched with a Cl $_2$  step. Finally, the silicon was etched with HBr/O $_2$ . The etch time directly determines the depth of the final structure. 40 s of etch time aims roughly for 250 nm depth of the spinodal structure.

Last but not least, the solgel and PMMA were removed with an 1% HF dip for 90 s and the final HUD structure was revealed. Initially, the lift off was supposed to be easily done by a heated acetone bath. However, this didn't work. Probably, the structure is too small and the acetone cannot penetrate the trenches. Hence the more toxic and time consuming method was chosen for this work.

The samples didn't undergo any additional cleaning steps and the wafers were used as-clean from the box. Base-pirana for instance modified the surface and different etching

#### **Chapter 2** Fabrication

**Figure 2.3:** Manual SCIL printing procedure. a) Vacuum-bonded 500  $\mu$ m Si wafer on sample holder. b) Spin-coating of 200 nm Solgel on the silicon sample. c) Orientation of the stamp. d) Lowering of the stamp. Pressure is applied manually with a rolling motion of the thumb. After 9 minutes of evaporation time, the stamp can be removed.

results have been observed. The trade-off between perfect reproducibility from thick to thin Si wafers and the risk of breakage of thin-Si due to additional steps needed to be found.

#### 2.2 Passivation Techniques

#### 2.2.1 Deposition of amorphous Al<sub>2</sub>O<sub>3</sub> and annealing

After the 1% HF dip, the samples were stored for several days in the clean room. No additional treatment or cleaning procedure was done prior to alumina deposition.  $Al_2O_3$  was deposited by a home-built atomic-layer deposition system (ALD). The deposition of alumina occurs atomic layer by atomic layer in alternating self-limited surface

ition of alumina occurs atomic layer by atomic layer in alternating self-limited surface reactions. The chamber is filled successively with precursors, that react with the surface till saturation. Each flush consists of a half-reaction. The deposition rate is 0.125 nm per minute and is conformal even on high aspect ratio 3D structures [17]. The samples were positioned on a hot plate at 250°C in the center of the chamber. The precursor used was trimethylaluminium (Al(CH<sub>3</sub>)<sub>3</sub>, Sigma-Aldrich). One cycle consisted of a 20 ms vapor pulse of Al(CH<sub>3</sub>)<sub>3</sub>, followed by a delay of 18 s, a pulse of 20 ms of water (MiliQ), another delay of 18 s, before starting over again. The base pressure of the chamber was kept at 1.1 mbar, controlled by an influx of  $N_2$  with respect to the vacuum pump. At these temperatures the hydrogen content is 1-2%at [17].

The samples were annealed on a hot plate in air at 420°C for 10 min. The 20  $\mu$ m samples were annealed loose without any carrier wafer. On the one hand, the glass carrier wafer would have cracked at such high temperature and risked to break the thin-Si, on the other, the PMMA and water bonds did not sustain the 250°C of the ALD and the thin-Si started

to levitate. After annealing they were again bonded either by water or PMMA to a carrier wafer.

#### 2.2.2 Deposition of amorphous SiO<sub>2</sub>

Amorphous  $SiO_2$  was deposited by plasmonically enhanced chemical vapor deposition (PECVD). The recipe consists of six steps. The main steps are an oxygen plasma clean (30 s at  $150^{\circ}$ C) to remove water and organic material from the sample surface, striking the plasma (10 s at  $150^{\circ}$ C) and finally the deposition of a-SiO<sub>2</sub> at  $150^{\circ}$ C (SiH<sub>4</sub> and N<sub>2</sub>O gas flow of 4.9 and 13.1 sccm, respectively), yielding a deposition rate of 14-15 nm per minute. The refractive index has been reported to follow literature values.

#### 2.2.3 Deposition of $SiN_x$

$SiN_x$  was deposited by plasmonically enhanced chemical vapor deposition (PECVD). The recipe is very similar to the one used for a-SiO<sub>2</sub>. The temperature of the chamber was kept at 100°C throughout the whole process and the SiH<sub>4</sub> and N<sub>2</sub>O gas flow were kept at 15.0 and 14.2 sccm, respectively. The growth rate is 16-17 nm per minute. The composition of the silicon nitride is  $Si_3N_4$  for a layer thickness of 250 nm. The refractive index is about 2.5% lower than literature values with an increasing deviation for thinner layers. An average value of  $n_{Si_3N_4} = 2$  is taken.

The finally produced samples are listed in Table 2.1.

| Si [µm]  | texture         | passivation                    | layer [nm] | method         |

|----------|-----------------|--------------------------------|------------|----------------|

| 500 & 20 | flat & spinodal | native                         | -          | -              |

| 500      | flat & spinodal | SiO <sub>2</sub>               | 5          | PECVD          |

| 500 & 20 | flat & spinodal | SiO <sub>2</sub>               | 10         | PECVD          |

| 500      | flat & spinodal | $Al_2O_3$                      | 5          | ALD            |

| 500 & 20 | flat & spinodal | $Al_2O_3$                      | 10         | ALD            |

| 500 & 20 | flat & spinodal | $Al_2O_3$ + anneal             | 10         | ALD + hotplate |

| 500 & 20 | flat & spinodal | $Al_2O_3$ + anneal             | 10         | ALD + hotplate |

|          |                 | $+Si_3N_4$                     | + 250      | + PECVD        |

| 500 & 20 | flat & spinodal | Si <sub>3</sub> N <sub>4</sub> | 250        | PECVD          |

| 500      | flat            | TiO <sub>2</sub>               | 10         | ALD            |

**Table 2.1:** Overview of the final passivation schemes. All samples have native oxide between the passivation layer and the silicon.

# 3.1 Evaluation of optical properties with UV-VIS spectroscopy

The UV-VIS setup used is a Perkin Elmer LAMBDA 750 UV/VIS/NIR spectrophotometer. The light source is a tungsten halogen lamp. High measurement stability is provided through a double-beam, double-monochromator design [33]. A switch in monochromators occurs at 860 nm, introducing some fluctuation in the collected data.

Two options are available to measure the absorption of a sample. First, the absorption is measured directly by hanging the sample in the center of the integrating sphere. Whereas this approach is very straight forward and accurate, a major drawback is poor beam incidence area control on the sample. If only the front side or certain areas of the sample want to be measured, the remaining of the sample needs to be covered.

In order to control the area exposed to the beam, the absorption can be calculated from separate transmission and reflection measurements by placing the sample at the front or back of the integrating sphere, respectively. Automatic baseline correction is available, however the baseline measurements need to be defined differently.

#### 3.1.1 Transmission measurement

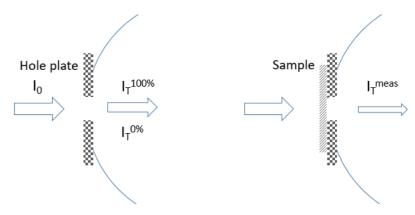

In transmission mode, the sample was placed where the beam enters the integrating sphere. An aluminium plate with a 6 mm hole was used to restrict the area of the sample exposed to the beam. The side of the plate facing the integrating sphere was whitened with a highly dispersive paint (labsphere 6080, theoretical reflective spectrum in Annex Figure 6.2), whereas the other in contact with the sample was covered with a non-conductive polymeric black paint. An iris was placed at the focal point of the beam in order to limit the beam diameter to fit the hole size. The baseline for 100% transmission ( $I_T^{100\%}$ ) is solemnly the hole plate, as shown in Figure 3.1, left. 0% transmission ( $I_T^{0\%}$ ) is measured by blocking the sample beam. During the measurement, the beam hits the sample and a share of the transmitted light enters the integrating sphere through the hole. As the hole is aligned with the iris-reduced beam and no important in-plane dispersion in the sample is assumed, most of the transmitted light reaches the integrating sphere.

#### **Chapter 3** Characterization

**Figure 3.1:** UV-VIS transmittance measurement scheme with baseline correction and beam area exposure control with an aluminium hole plate. Left: Open hole corresponding to 100% transmittance baseline measurement. Right: Sample measurement configuration.

Analytically this can be expressed as:

$$T^{sample} = \frac{I_T^{meas} - I_T^{0\%}}{I_T^{100\%} - I_T^{0\%}} = \frac{I_T^{sample}}{I_0}$$

(3.1)

Where  $I_T^{sample}$  corresponds to the true intensity transmitted by the sample after subtracting any background light and  $I_0$  the maximal light intensity reaching the integrating sphere.

#### 3.1.2 Reflection measurement

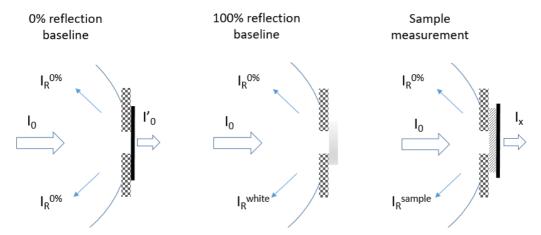

In reflection mode, the sample was placed at the back of the integrating sphere at a small constant angle with respect to the source. The hole plate was again placed accordingly to the beam, the whitened face facing the integrating sphere. The baseline for 100% reflection  $(I_R^{100\%})$  was measured using a silver mirror (Thorlabs PF10-03-P01), shown in Figure 3.2, center. The provider indicates a spectral reflectance of about 97%. Initially, 100% reflection was measured using a piece of the same material the sphere is made from. However, when measuring the reflection of the mirror with respect to the white piece, it proved 10% more reflective and was therefore chosen as the reference. The holder of the mirror introduced a 1 mm gap between the hole plate and the mirror surface. 0% reflection would ideally be measured by open space (open hole, mimicking a black body), or, as suggested by the provider, using a blackened hood over the sample. However, when measuring a black tape with respect to the open space, a reflection of -100% was obtained. Therefore, a thick layer of tape was used as 0% reflection  $(I_R^{0\%})$  (Figure 3.2, left). When measuring the sample, the same black tape is placed directly behind. Without tape the measured reflectance was

**Figure 3.2:** UV-VIS reflectance measurement scheme with baseline correction and beam area exposure control with an aluminium hole plate. Left: black tape for 0% reflectance baseline measurement. Center: Silver mirror for 100% reflectance. Right: Sample measurement configuration, where black tape is placed behind the sample.

overestimated for very thin samples. The final configuration is shown in Figure 3.2, right.

Considering that 100% reflection is the sum of whatever is reflected by the open integrating sphere  $(I_R^{0\%})$  and the reflection of the mirror:  $I_R^{100\%} = I_R^{mirror} + I_R^{0\%}$ , and the measured intensity is the sum of the open integrating sphere and the sample:  $I_R^{meas} = I_R^{0\%} + I_R^{sample}$ , then the relative measured reflectance is:

$$R^{meas} = \frac{I_R^{meas} - I_R^{0\%}}{I_R^{100\%} - I_R^{0\%}} = \frac{I_R^{sample}}{I_R^{mirror} + I_R^{0\%} - I_R^{0\%}} = \frac{I_R^{sample}}{I_R^{mirror}} = \frac{I_R^{sample}}{\alpha_\lambda \cdot I_0}$$

(3.2)

Where  $\alpha_{\lambda}$  is the spectral reflectance of the mirror. The reflectance of the sample can be expressed as:  $R^{sample} = \alpha_{\lambda} \cdot R^{meas}$ .

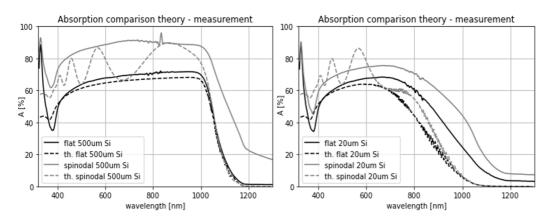

#### 3.1.3 Comparison with analytical results

As a comparison to the experimental data, the stack of layers was simulated by implementing the Fresnel equations for an unpolarized and perpendicular incident light beam. Three different scenarios were considered:

- Flat silicon: Si sandwiched between two semi-infinite air layers with n = 1

- Patterned silicon: Si + HUD layer with 280 nm thickness and refractive index determined from equation 1.1, sandwiched between two semi-infinite air layers

#### **Chapter 3** Characterization

• The previous two cases + a dielectric layer with the respective refractive index.

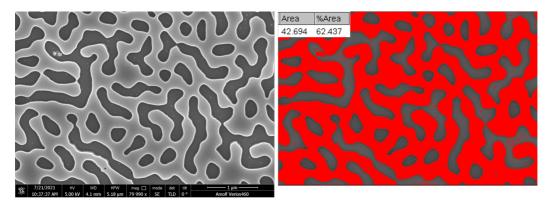

For simplification, the spectral dependence of the refractive index for the passivation layers was neglected. The filling fraction for the HUD spinodal structures were determined from SEM images without tilt, using a pixel count feature of a image processing software, as shown in the appendix, Figure 6.4.

The post-processing included a smoothing of the curves by doing an averaging over 10 points and a correction of non-perfect reflection of the silver mirror.

#### 3.2 EIS and CV

#### 3.2.1 Setup and measurement technique

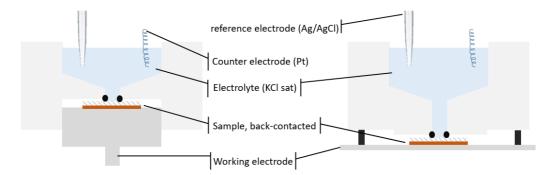

Electrochemical impedance spectrometry (EIS) was conducted using a Potentiostat (SP-300 by BioLogic) and a customized electrochemical cell. The cell offers two ways to back-contact the samples. First, the sample can be directly contacted through a conductive holder that is used to screw the sample into the cell until in tight contact with the O-ring (Figure 3.3, left). This was ideal for 500  $\mu$ m silicon samples that wouldn't break under the minor tangential forces applied when screwed into tight contact with the O-ring. In this setup the native oxide was scratched on the backside with a diamond tip and eutectic InGa was applied for contacting. In order to improve the contact surface, a copper tape stack was used in direct contact with the InGa.

**Figure 3.3:** EIS setup using a Ag/AgCl with 3M KCl solution as reference electrode and a platinum coil as counter electrode. The electrolyte is a saturated KCl solution, in contact with the back-contacted sample connected to the working electrode. The solution is confined using a leak-proof O-ring.

Second, the sample can be pressed against the O-ring by mounting the cell vertically onto a conducting holder, as shown in Figure 3.3 (right). In this case, the forces acting upon the sample are only vertical and this configuration is thus adapted for thin-Si. A with 30 nm Al covered silicon piece was used as a substrate. The Al was deposited with an

E-beam system from Polyteknik. In contrast to the 500  $\mu$ m Si, on the thin Si the native oxide on the back side needed to be removed chemically by HF, not mechanically. In order to protect any layers deposited on the front side, a HF resist (Allresist, AZ1518 SX AR-PC 5000/40) was spin-coated before the HF dip. Afterwards, a 30 nm Al layer was deposited on the etched surface. Finally, the HF resist was removed in an acetone bath. The Al-contacted thin-Si was bonded with water onto the Al-covered substrate. The latter was sandwiched against the O-ring with four screws, tightened equally.

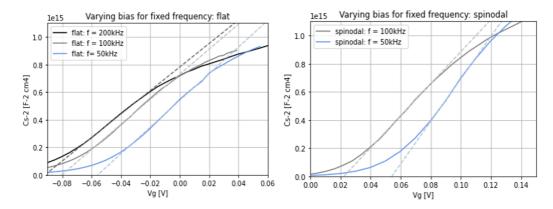

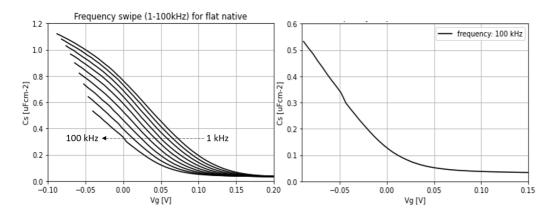

A three electrode scheme was used. The reference electrode used was an Ag/AgCl (3M KCl) (BASI, RE-5B) and the counter electrode a platinum coil. Both electrodes were immersed equally in a saturated KCl solution. The parameters for EIS were chosen as described by Mikulik *et al.* (2018) and Meng *et al.* (2017) [27, 28]. The frequency range for EIS was 1-100 kHz with an AC oscillation amplitude of 10 mV and 7 frequency steps. By first conducting an IV-measurement, the substrate voltage range was determined for every sample, such that no current would flow. The open-circuit potential was assessed before starting the measurement. As the equipment run into technical issues by getting stuck at random moments throughout the cyclic frequency swipes, single-frequency measurements were done afterwards.

#### 3.2.2 Analysis of the data

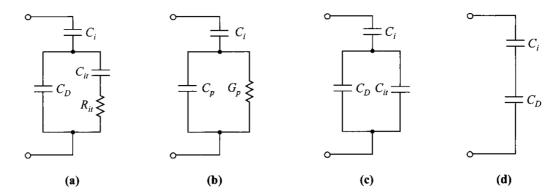

For the analysis of EIS data, different methods are being used. Essentially, they depend on the frequency range accessible by the setup. The Low-Frequency Capacitance Method uses the low-frequency equivalent circuit (Figure 3.4, c) [21, 38, 42], the High-Frequency Method uses the high-frequency equivalent circuit (Figure 3.4, d) [23, 31, 38, 41] and the High-Low-Frequency Capacitance Method is based on a combination of both [7, 32, 38]. It is often completed by conductance-voltage measurements for lifetime calculations [6, 7, 23, 27].

The EIS setup at hand has an upper limit of 200 kHz and the low frequency limit cannot be reached. Hence, the high-frequency method by Terman is to be implemented [41]. In order to understand the method, some basic relations shall be introduced here.

# 3.3 Measurement of Interface Traps in silicon using MOS capacitors: the Terman method

The system of an insulator and semiconductor described by equation 1.5 can be extended to an equivalent circuit, incorporating the influence of the interface trap states in silicon. A capacitance  $C_{it}$  and resistance  $R_{it}$  are included, both functions of energy. The interface-trap lifetime is defined as  $\tau_{it} = C_{it} \cdot R_{it}$ , describing the response of the traps to the applied

#### **Chapter 3** Characterization

frequency. In Figure 3.4, a the representative circuit is shown.

**Figure 3.4:** Equivalent circuits describing the MOS system including interface traps.  $C_{it}$  and  $R_{it}$  are the capacitance and resistance associated with the interface traps. a)  $C_{it}$  and  $R_{it}$  in parallel with the semiconductor depletion capacitance. b) Conversion into a frequency-dependent capacitance  $C_p$  in parallel with frequency-dependent conductance  $G_p$ . c) Low-frequency limit. d) High-frequency limit [38].

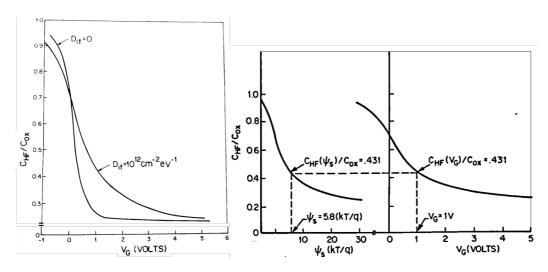

In the high-frequency limit, the influence of the interface trap states can basically be ignored (Figure 3.4), as the traps cannot respond fast enough to the high frequency and the analytical expression for the high-frequency capacitance  $C_{HF}$  reduces to equation 1.5 [38]. For a certain depletion layer capacitance  $C_D$ , the high frequency capacitance of a MOS capacitor will be the same as that of an ideal capacitor without interface traps. However, besides the effect of the two additional circuit elements  $C_{it}$  and  $R_{it}$ , the interface traps affect as well indirectly  $C_D$ . They take up some of the charges, that otherwise would have been used to deplete the layer. Hence,  $C_D$  is lowered, resulting in a lower surface potential or less band bending. Therefore, the measured capacitance-voltage relation will as well be altered in the high-frequency case [31, 38]. This causes a stretch and distortion of the ideal C-V curve 3.5, left) [31].

At same band bending (surface voltage)  $\Psi_S$ ,  $C_{HF}$  will be the same as  $C_{HF}^{ideal}$ . Therefore, if  $\Psi_S$ , corresponding to a certain  $C_{HF}^{ideal}$ , can be determined, and the applied voltage V corresponding to the same  $C_{HF}$  with traps measured, the band bending  $\Psi_S$  vs. V relation can be established, as illustrated in Figure 3.5. There, all the information about the interface trap level density is contained [31].

In order to express the change of the semiconductor surface voltage  $\Psi_S$  with respect to

the density of interface traps,  $\Psi_S$  is isolated from the applied voltage using, equation 1.5:

$$\frac{d\Psi_S}{dV} = \frac{C_i}{C_i + C_D(\Psi_S) + C_{it}(\Psi_S)} \tag{3.3}$$

And hence:

$$C_{it}(\Psi_S) = C_D \left[ \left( \frac{d\Psi_s}{dV} \right)^{-1} - 1 \right] - C_S(\Psi_S)$$

(3.4)

And using equation 1.6 in 3.4,  $D_{it}$  can be determined. This results in the analytical expression:

$$D_{it} = \frac{C_i}{q^2} \left[ \left( \frac{d\Psi_S}{dV} \right)^{-1} - 1 \right] - \frac{C_D}{q^2}$$

(3.5)

For a certain  $C_D$ -V plot, the band bending  $\Psi_S$  for silicon can be determined from theory and equation 3.5 finally gives the interface trap state density  $D_{it}$ .

**Figure 3.5:** Left: C vs. V curve stretch due to the presence of interface trap states. Right: Illustration of the implementation of the Terman high-frequency method, determining  $\Psi_S$ -V relation for the calculation of the interface trap capacitance. *Courtesy of Nicollian et al.* (1982), p.328 [31].

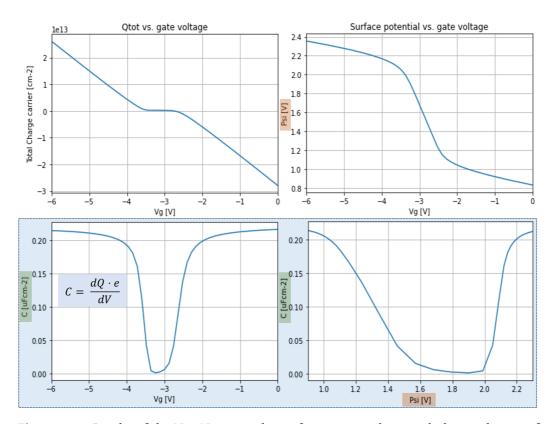

#### 3.3.1 Ideal $\Psi_S$ vs. V curves for the high-frequency Terman method

In order to get the capacitance vs. surface potential curves (C- $\Psi_S$ ), the NextNano software package was used [4] in order to solve the 1D Schrödinger-Poisson equations. A great tutorial is made available by the developers [10] and was adapted accordingly.

#### **Chapter 3** Characterization

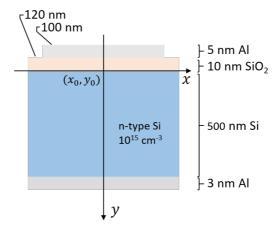

The Si/passivation layer/electrolyte MOS capacitor was approximated as a Si/passivation layer/Al MOS capacitor with a Schottky contact. For silicon with 10 nm of a-SiO<sub>2</sub> a value of  $\phi_b = 0.7$  eV was used as the Schottky barrier height [5]. The doping concentration found via the Mott-Schottky plot, equation 1.8, was used as the number of charge carriers. It was set to  $10^{15}$  cm<sup>3</sup> for the results presented. A similar approach is hinted by Mikulik *et al.* (2018). The corresponding MOS capacitor is shown in Figure 3.6.

The outcome of the simulation was dependent of the gate voltage range. The voltage range of (-6.0,0.0) V was chosen such that the potential with charge inversion was in the middle of the range. The simulation gives the total charge per cm at every applied voltage point. A partial derivative  $\partial Q/\partial V$  allows to plot C-V. The surface potential can be accessed by measuring the electrostatic potential at the semiconductor-oxide interface as a function of applied V, transcribing the values at x,y = (0,0). A 1D-slice is implemented at the corresponding coordinates (x = 0, on a slice of 2 nm depth) [10].

In order to plot the curves for different insulators (dielectrics), the SiO<sub>2</sub> thickness can be scaled to an equivalent oxide thickness ( $d_{eq}$ ) by expressing the SiO<sub>2</sub> thickness relative to the new insulator permittivity:  $d_{eq} = d_{SiO_2} \frac{\epsilon_(SiO_2)\epsilon_0}{\epsilon_(insulator)}$  [13, 44, 45].

Figure 3.6: Implemented MOS capacitor for the simulation in the NextNano software package.

#### 3.4 Lifetimes measurements

First, lifetimes were to be determined by photoluminescent decay measurements. The device used is a LED-based PL system by greateyes (LumiSolarCell System). The setup is very user friendly. The samples were simply be placed on the stage and the integration

times were adjusted incrementally, starting from 1 s up to 60 s. The light source was 660 nm light source, hence far enough from the bandgap of silicon such that the silicon bandgap transitions can be excluded.

The detected PL signal was very small even with long integration times. Hence a antireflection filter was used in order to access the tail of the signal.

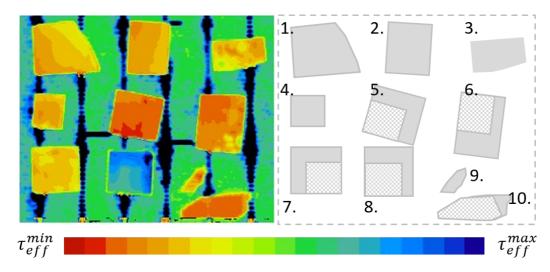

Another attempt was made with a system from SemiLab (WT-2000), operating with microwaves, detecting the photoconductance decay carrier lifetimes. The sample is lifetime-mapped with a laser wavelength of 904 nm. However, due to diverse technical discrepancies, the the system is not able to give absolute lifetimes, but serves still to give a relative lifetime comparison between sample regions.

## 4.1 Fabrication of the samples

#### 4.1.1 SCIL fabrication and etch parameters

errors can occur at every step and every sample should be checked on depth and quality before further processing. Figure 4.1 shows one unsuccessful imprint, where the edges are not sharp and the etching seems to have rounded the corners. This could be due to insufficient solgel height after spin-coating for example. As a consequence, the breakthrough etch of 120 s might be too long, leaving the edges already rounded and exposing facets that would be etched quicker during the direction selective Si etch with HBr. The etch parameters were defined as 120s CHF<sub>4</sub> + 40s HBr/O<sub>2</sub> + 90s HF after having done a HBr time comparison of 70 and 40 s. 40 s HBr silion etching yielded around 240  $\pm$  20 nm depth for the 20  $\mu$ m and 500  $\mu$ m silicon and was chosen as the standard etch time for all the samples. The depths were determined by mean of tilted SEM images (30°). The HF times were studied in a 1% HF dip series as shown in Figure 4.2, increasing the time from 45 to 105 s (a-d). The pattern wasn't influenced by the dipping neither in aspect ratio, nor in edge quality. Apparently, 40 s HF dip is enough to remove all the solgel. As the silicon doesn't seem influenced by the HF step, longer HF times were maintained such that no

The SCIL process was very straight forward and easily assimilated. Nevertheless, small

The 10 and 20  $\mu$ m silicon samples that were bonded to a carrier wafer, were more difficult to image. More charging of the surface made it harder to have a good image acquisition. Furthermore, since the carrier wafers were larger than the imaged 500  $\mu$ m samples and spanned often over two carbon tape pieces for fixation. This resulted in important drift as the residual elastic deformation in the tape was relaxing. Nevertheless, the depth and quality of the HUD pattern were perfectly reproduced on the thin-Si wafers.

residual solgel was risked if during spin-coating the layers resulted thicker for example.

#### 4.1.2 Passivation of the samples

Imaging of the passivated layers was used only for occasional quality control. In Figure 4.3 a sample with 250 nm  $Si_3N_4$  is shown. The deposition of  $SiN_x$  is novel for this PECVD setup and the deposition of thin layers needs to be further explored. Namely, the increasing deviation in refractive index with decreasing layer thickness suggests that the deviation in stoichiometry might increase and the optical properties no longer are guaranteed.

**Figure 4.1:** Unsuccessful spinodal pattern after SCIL imprint of a 500  $\mu$ m Si sample and etch process: 120s CHF<sub>4</sub> + 40s HBr/O<sub>2</sub> + 90s HF.

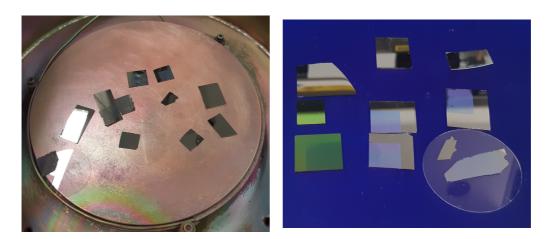

The relatively thick  $\mathrm{Si_3N_4}$  layer resulted clearly in a greenish appearance (appendix Figure 6.5). The handling of the ALD system was as well straight forward. However, the system needed often several restarts as it struggled with the connection to all sensors and control devices. The passivation of thin-Si samples was a bit trickier. It was apparent that 20  $\mu \mathrm{m}$  Si samples, that were bonded by PMMA to the carrier wafer, as well as the water bonded samples would start to levitate under the influence of the heat of the chamber and the important air flows of pumping/flushing, displacing them all over the hot plate (appendix Figure 6.5). The ALD chamber isn't in a clean environment and contamination is unavoidable.

The thin wafers were surprisingly resistant to the manipulations and a wast majority survived. Most wafers broke during debonding when surface tensions were involved. That was enough to induce cracks. Grabbing them with tweezers when they were dry, was a rather safe way to handle them.

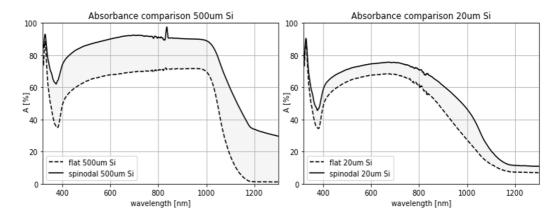

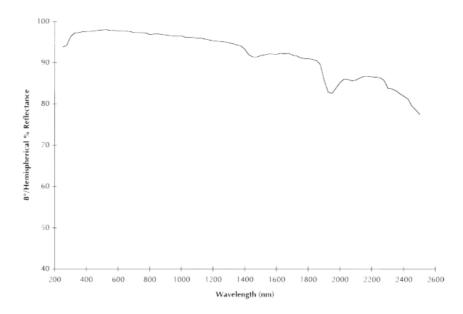

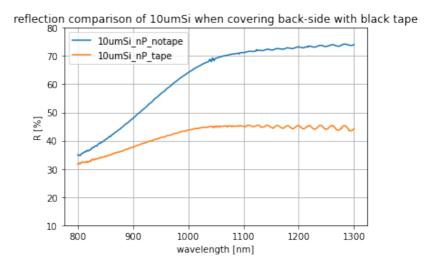

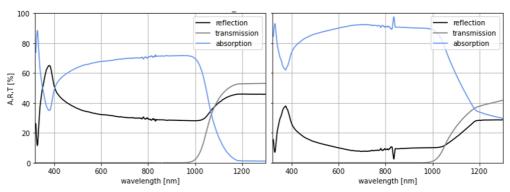

## 4.2 Optical properties and absorption measurements